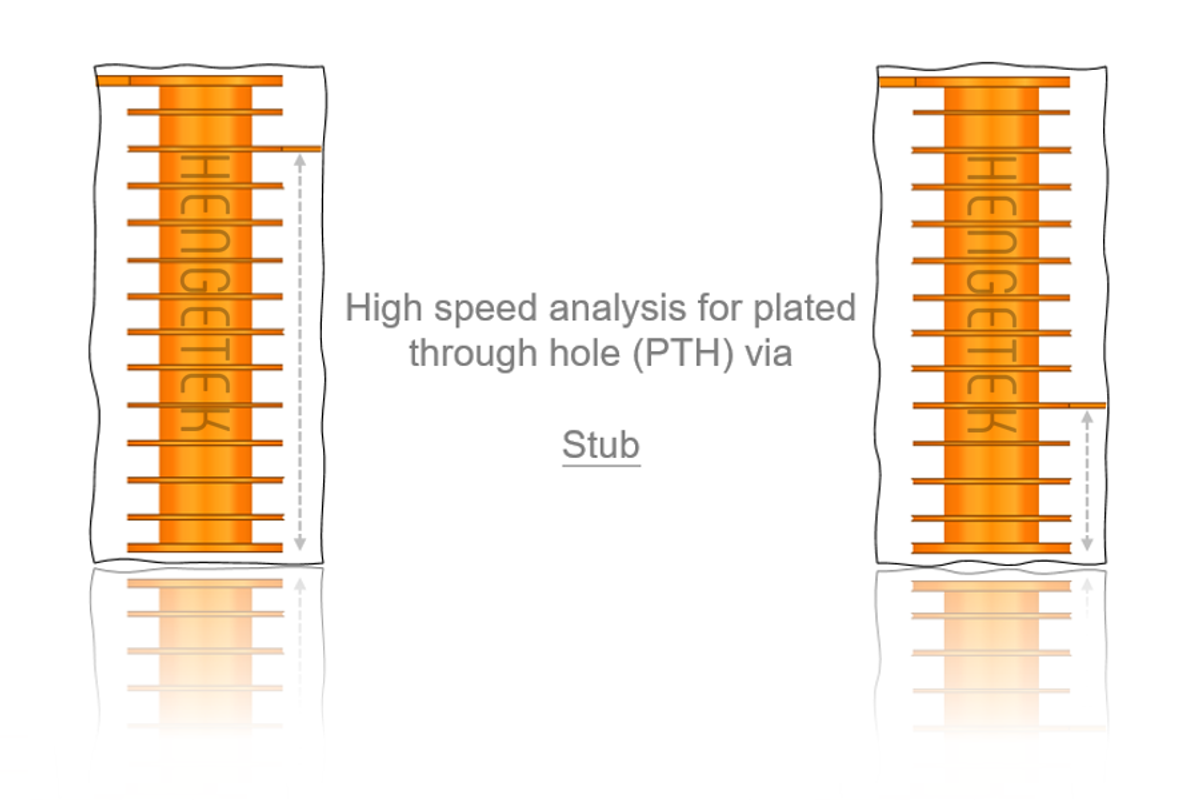

當產品整個系統電路架構 (electronic circuit schematic design) 確認後,便可開始規劃該如何走線佈局 PCB (printed circuit board layout design),此階段要考慮板內 (board outline) 的空間配置和各信號間預防耦合干擾 (signal coupling) 等考量,故 layout 走線時將透過 Via 過孔換層來分配各組信號線前往所安排的區域。此專題藉由一個 (14Layers / 1.6mm / PTH via / Layer 1 trace in / Layer 3 trace out) 和一個 (14Layers / 1.6mm / PTH via / Layer 1 trace in / Layer 10 trace out) 兩種不同層出線的電鍍通孔 (plated through hole) 來觀察看看,信號走線 (signal trace) 從第三層和第十層出來的結構差異,所產生不同長度的無用殘樁影響 (stub effect)。

針對電鍍通孔 (Plated Through Hole) PTH via 在不同層走線規劃所造成的阻抗差異,從 TDR (Time-Domain Reflectometry) 阻抗曲線可以觀察到,確實在未優化的過孔所產生的無用 Stub 殘樁長度其阻抗差異非常明顯,從第三層走線出去的 (L3 stub) 殘樁較長,阻抗值最低點來到 20.24 ohm,第十層走線出去的 (L10 stub) 殘樁較短,阻抗值最低點來到 31.38 ohm,兩種不同層走線的 PTH via 過孔結構所造成的殘樁效應 (stub effect) 影響顯然不能忽視。對於未經過優化的 Via 過孔很容易造成阻抗不連續性 (impedance discontinuity) 的問題,這將導致高速信號在傳輸的過程中於此處出現很大的反射 (reflection) 現象,隨著傳輸路徑上的阻抗不連續點增加,信號傳到了末端時眼圖波形可能已經有閉合失真的狀況,接收端 (receiver) 將無法正確讀取出驅動端 (driver) 所傳輸的指令數據。

在整個 25 GHz 頻率範圍的S11回波損耗 (return loss) 曲線,從第十層走線出去的 PTH via 過孔 (L10 stub) 其無用的殘樁長度較短,全頻段的S11回損皆小於殘樁長度較長的 PTH via 過孔 (L3 stub),在 10 GHz 頻點位置上的回損 (L10 stub & L3 stub) 分別為 ( -6.06dB & -0.75dB )。雖然較短殘樁的 PTH Via 過孔走線確實減小了回損,但其整體S11回損的表現還是非常不理想。

至於S21插入損耗 (insertion loss) 曲線的表現,從第三層走線出去殘樁長度較長 的 PTH via 過孔 (L3 stub),在接近 10.56 GHz 頻點上出現了一個 -24.10dB 很大的諧振,此位置附近插損極其嚴重不得不多加注意,若所傳輸的信號帶寬落在此處也將會影響到接收端波型。反觀從第十層走線出去殘樁長度較短的 PTH via 過孔 (L10 stub),明顯改善了許多而且S21插損曲線也相對小且平緩。

經由上述在時域 (time domain) 與頻域 (frequency domain) 所觀察到的結果,殘樁效應 (stub effect) 對於電鍍通孔 (Plated Through Hole) PTH via 性能影響甚大,殘樁長度越長所造成的阻抗不連續性 (impedance discontinuity)、回波損耗 (return loss)、插入損耗 (insertion loss) 等各項指標越惡化,對於高速信號的 SI (signal integrity) 信號完整性有很嚴重的影響,不得不多加注意。