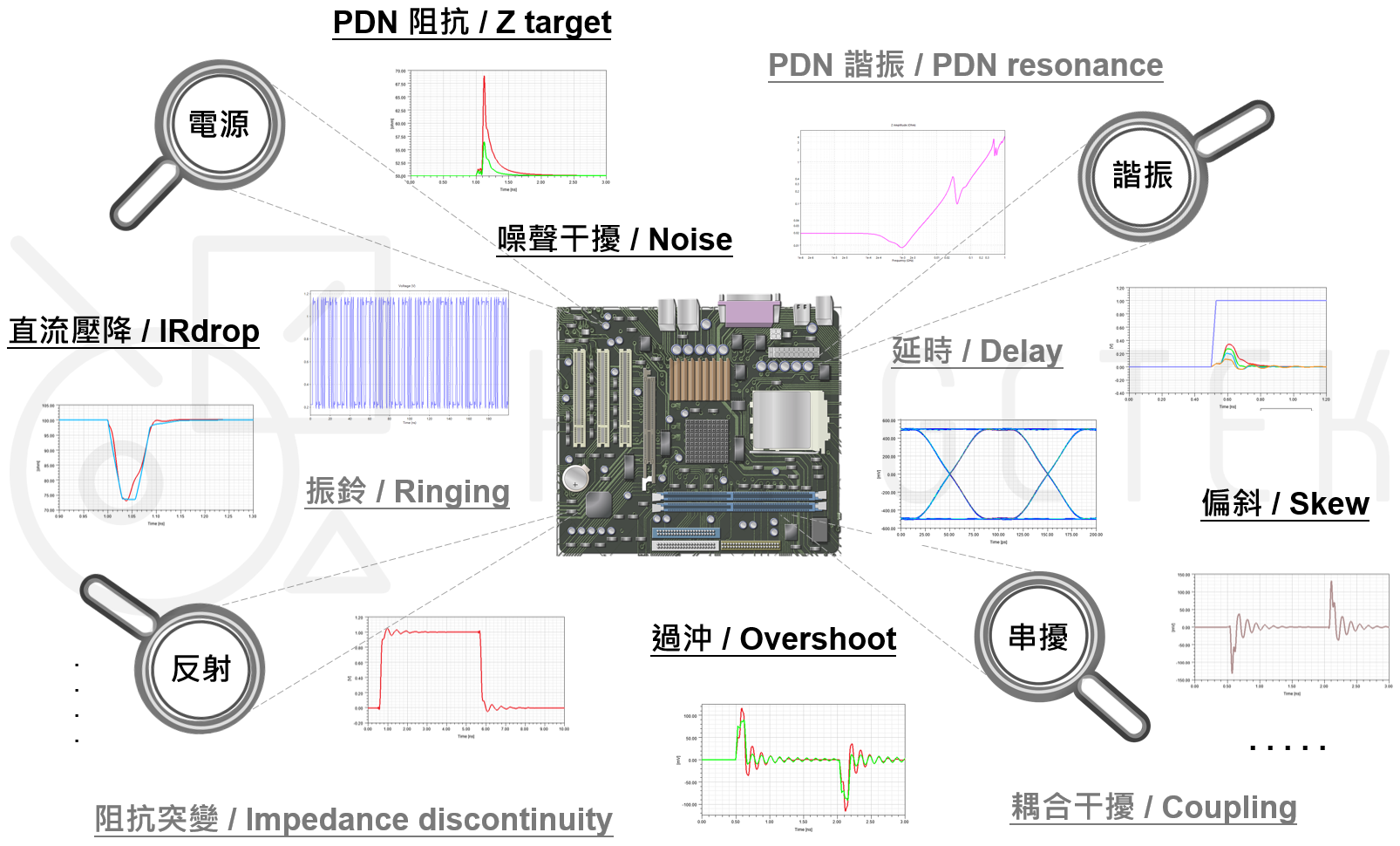

隨著科技的進步,信號速率越來越快、元器件密度越來越高、 PCB尺寸要求越來越小,過往所面臨的信號完整性 (Signal Integrity ; SI) & 電源完整性 (Power Integrity ; PI) 問題如: 反射 (Reflection)、振鈴 (Ringing)、過沖 (Overshoot)、下沖 (Undershoot)、邊沿不單調 (Non-monotonic)、串擾 (Crosstalk)、SSN噪聲 (Simultaneous Switching Noise)...等現象也更加惡化,若不加以抑制並控制住風險,將嚴重損害整體系統性能。

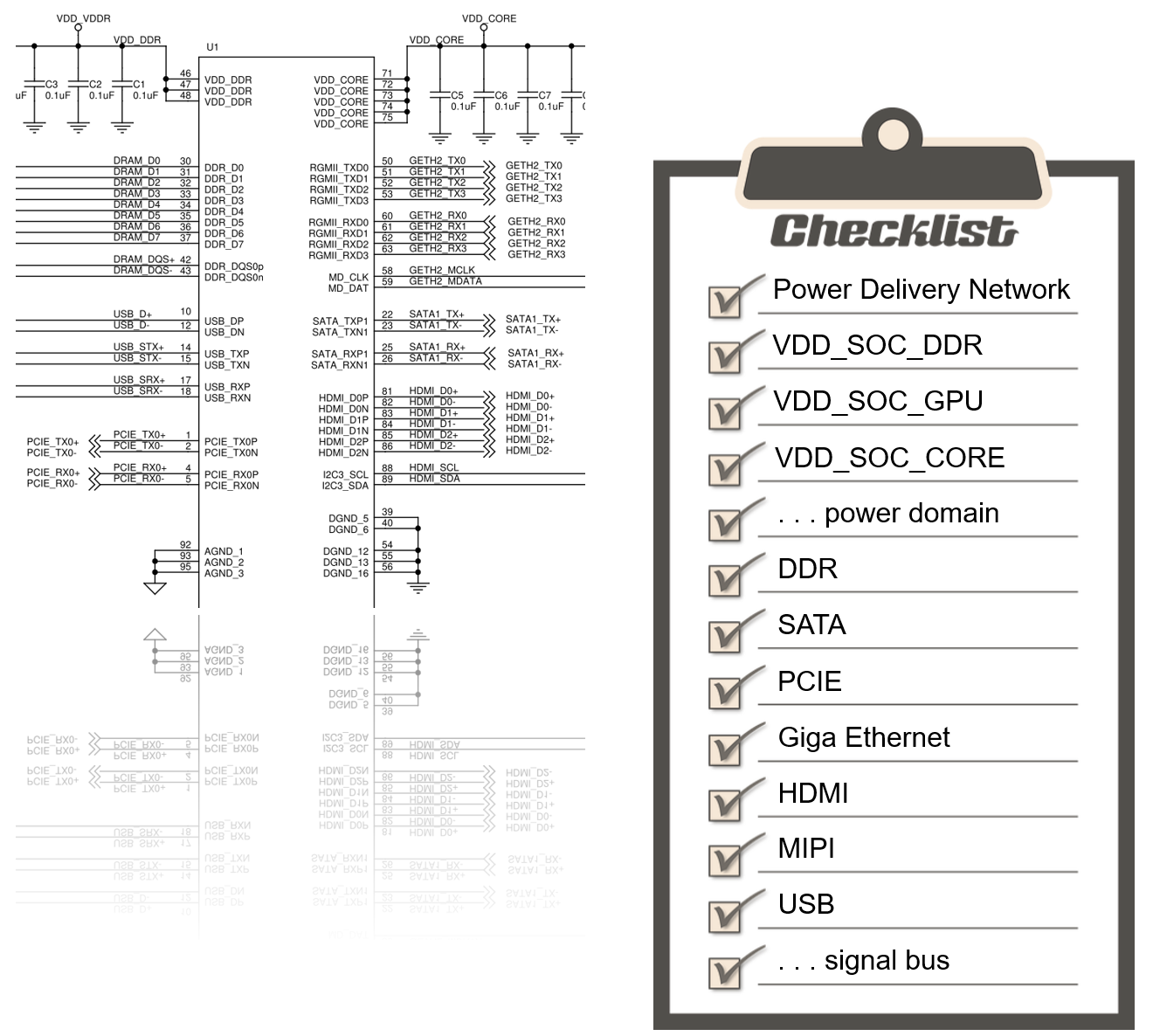

詳細排查每個電源域的直流壓降 (IR drop) & 頻域阻抗 (Z target),與每一組高速信號總線 (Serial/Parallel Bus) 的反射 (Reflection)、耦合干擾 (Coupling) & 端接/拓撲 (Terminal/Topology) 結構,其必要性變得重中之重,將有助於『提高研發成功率』、『縮短研發週期』、『降低研發成本』。